7.1 Generation of Impulse Test Voltages

7.1.1 Classification of Impulse Test Voltages

LI over-voltage caused by 200 kA LI current pulse of different front times superimposed on the negative AC voltage peak at a GIS (above) and at a power transformer (below)

Example for an SI over-voltage

SI breakdown voltage of long air gaps depending on the time-to-peak

For on-site testing, also oscillating impulse voltages (OLI; OSI) are applied (IEC 60060-3:2006). OLI and OSI test voltages can be generated with a generator of efficiency factors about twice of those for LI and SI voltages (see Sect. 7.1.3). Even if this is made for easier transportation and handling of the test system, it should be mentioned that the used OLI and OSI test voltages represent quite well the related over-voltages (compare with Figs. 7.1 and 7.2). Also the so-called “damped alternating voltage” (IEC 60060-3:2006; DAC) used for PD testing of cable systems in the field—is an OSI voltage. OSI voltages can also be generated by test transformers (see Sect. 7.1.4).

Last but not least, it should be mentioned that in case of disconnector switching in SF6-insulated systems (GIS), over-voltages faster than LI over-voltages are generated. They are represented by fast front test voltages (FFV) and generated by switching the disconnector in the GIS under test (see Sect. 7.1.5).

7.1.2 Basic and Multiplier Circuits for Standard LI/SI Test Voltages

7.1.2.1 Basic RC Circuit

Basic equivalent circuit for impulse voltage generation. a Equivalent circuit diagram. b Potential diagram

Note In addition of the circuit of Fig. 7.4a, a second basic circuit which has the tail resistor not before, but after the front resistor, is sometimes discussed in textbooks. This circuit has a lower efficiency factor. Therefore, it is not used practically and not discussed here.

Note The analytical calculation of the time parameters of impulse voltages and their efficiencies is given in older textbooks. Today, the analytical calculation is replaced by well-adaptable and commercially available software programs. This enables also the more detailed consideration of the characteristics of the test object and the stray capacitances in the test room and delivers more precise results.

Whereas the maximum charging voltage of a generator depends on the required test voltages, the impulse capacitance must be selected according to the expected total load (basic generator load plus test object load), to guaranty Ci ≫ Cl.

7.1.2.2 Multiplier RC Circuit

Multi-stage impulse generator of n = 6 stages. a Multiplier circuit (explanations in the text). b Impulse generator

The term V0n max = n · V0max is called the cumulative charging voltage of the generator and usually used as the rated voltage of the impulse test system because V0n max > Vin max one has to be careful with the valuation of rated voltages for impulse test systems. It is always necessary to know the efficiency factor for all impulse voltage shapes of interest for the calculation of the related output voltages additionally.

After the calculation of the circuit elements of the basic circuits, the above Eq. (7.5) are used for the determination of the multi-stage generator by re-transformation. The thermal design of the resistors—especially of the front resistors—determines the allowable impulse voltage repetition rate. The resistors are heated by the impulse current, which is flowing in case of the impulse voltage generation and should sufficiently cool down until the next impulse appears. A defined maximum temperature of the resistors must not be exceeded.

Triggering of impulse voltage generators. a Trigatron spark gap. b Principle of the trigger range

LI voltage generation circuit considering the inductance a Equivalent circuit diagram with inductances. b Over-shoot superimposed on LI voltages (schematically)

The modular design of multi-stage generators is helpful for later extension to higher voltages by additional stages. It enables also the parallel connection of stages for higher impulse energy at lower voltages [Fig. 7.5a, red short-circuit bars (SCB)] as they are, e.g. required for testing the low-voltage winding of power transformers or medium-voltage capacitors. Also impulse test currents can be generated by impulse voltage generators with parallel stages.

7.1.2.3 Consideration of the Inductance in the Circuit

Inductances to be assumed for HV leads

Length of HV lead (m) | Single wire, d = 2 mm (μH/m) | Metal foil, w = 10 cm (μH/m) | Metal tube, d = 10 cm (μH/m) | Metal foil, w = 50 cm or 2 foils with spacer in between (μH/m) |

|---|---|---|---|---|

1 | 1.37 | 0.70 | 0.59 | 0.40 |

10 | 1.83 | 1.26 | 0.96 | 0.84 |

Inductances form oscillating circuits with the capacitances and cause damped oscillations superimposed on the aperiodic pulses. The damping depends on the front resistor. This is several 100′ Ω for SI voltages and suppresses the oscillations completely. The more or less damped oscillations and the “over-shoot” (only less than one period of the oscillation) are found at LI voltages only, because the LI generator is equipped with front resistances of few 10′ Ω (Fig. 7.7). There are internal inductances of the generator and external of the test object and its connections.

Internal inductances Li are those of the capacitors, the resistors and the connections between them. For estimations, the inductance for 1 m of the loop (e.g. green path in Fig. 7.5a) is about 1 μH. The reduction in the internal inductance of a generator requires its compact design with a loop as short as possible. A good generator should have an internal inductance of Li < 4 μH per stage. Usually, the user cannot influence the internal inductance of the generator easily. When only a part of the stages is sufficient to generate the necessary voltage (so-called “part operation”), the loop should be short and should exclude the not-used part of the generator and of the basic load (voltage divider). For very old generators, one should check the inductance of the front resistors: The front resistors must be designed with low inductance, which can be reached by a bifilar winding. This means that two isolated, close together arranged wires are wound on a fibreglass tube in opposite directions. The magnetic fields of the wires have opposite directions and compensate each other to a remaining inductance which corresponds to the length of the resistor tube. A second possibility is a resistor band where the insulated resistance wires are woven into a fabric as a meander. Resistor bands are commercially available. The inductance of resistors can also be reduced when, instead of a single resistor, two or more parallel resistors are applied resulting in the same resistance.

External inductances Le are those of the test object (even if this mainly a capacitance), the HV lead to the test object and the voltage divider as well as those of the earth return. HV lead and earth return shall be especially very short and can often be influenced. With increasing LI test voltage, the distances between generator and test object become longer and oscillations and over-shoot cannot be controlled in testing UHV equipment (see Sect. 7.3). Up to a certain degree, also the inductance of the circuit can be reduced by an appropriate selection of the geometry of the HV lead. Table 7.1 gives some inductances depending on the shape and the length of the connection. Never a thin wire should be used for the HV lead or the ground return, because its inductance is higher than those of copper foil of a width w ≥ 10 cm or metallic tube of a diameter d ≥ 10 cm. A further reduction can be reached with a wider foil or two parallel foils and spacers with a distance d in between. Also quite useful is the application of the mentioned resistor bands as HV lead and external damping resistor to the test object. To maintain the impulse shape, the internal front resistor must be reduced, but the external resistor increases the damping efficiency including the efficiency factor.

Equivalent circuit diagrams of over-shoot compensation units. a Parallel compensation unit. b Series compensation unit

The series compensation unit (Fig. 7.8b; Wolf and Voigt 1997) prevents the penetration of higher-frequency contributions to the load capacitance which includes the test object. The series connection of compensation resistance Rc and compensation inductance Lc must be adjusted to that of the front resistor Rf and internal inductance Li. Also the compensation capacitor Cc has to be related to the load capacitance Cl. The necessary adjustment covers a certain range of load cases, but if fine tuning is required, the compensation unit must be adapted. For larger impulse generators, the series compensation unit can be distributed to the different stages of the generator (with elements of the stage voltage, e.g. 200 kV) and without components of high-rated voltage (e.g. 3000 kV).

Parallel compensation unit in combination with voltage divider and chopping gap

7.1.2.4 Some Details of the Design of Impulse Voltage Test Systems

Components of an LI/SI test voltage system

Typical circuits for impulse voltage generators. a Unipolar charging (e.g. 200 kV). b Symmetric charging (e.g. ±100 kV)

Impulse voltage generators for unipolar and symmetric charging. a Generator with unipolar charging (Courtesy of Haefely, Basel). b Generator with symmetric charging. c One-stage of a multi-stage generator (inside view). d Cross section of a generator with symmetric charging

Reproducibility of LI voltage shapes independent on peak voltage value

Chopped lightning impulse generation. a Chopped lightning impulse (LIC) voltage. b Circuit of two modules of a multiple chopping gap. c Multiple chopping gap for 1200 kV (six single gaps)

The LIC test voltage is generated as an LI test voltage described above and then chopped by a separate chopping gap. For LIC voltages up to about 600 kV, a usual sphere-to-sphere gap can be used; for higher voltages, multiple chopping gaps become technically mandatory (Fig. 7.14b, c). The voltage collapse of a multiple spark gap is much faster than that of a single large sphere gap. The chopping gap consists of in-series-connected sphere-to-sphere gaps, usually one gap for one stage of the generator. One sphere of each gap is fixed and arranged at a fixed insulating column. The other one—on suitable insulating support—is moveable by a motor drive and can be adjusted for the relevant voltage value. The parallel capacitor column controls the voltage distribution linearly (Rodewald 1972). This column might also be used as a damped capacitive voltage divider, which is usually a separate component (see Sect. 7.5). The instant of the chopping can be triggered as described above for the generator (Fig. 7.6). Also the combination with an over-shoot compensation unit is applied (Fig. 7.9).

Electrodes for the HV components of LI/SI voltage test systems. a Necessary clearance D around a LI/SI generator. b Test system only for LI voltage generation (2000 kV), c Test system 1800 kV for LI/SI voltage generation at limited clearance to the ceiling. d Outdoor test system 4200 kV for SI and LI voltage generation.

Courtesy of KEPRI, Korea

Note This clearance should not be mixed up with the clearances for the test object according to Fig. 2.1. The clearances there consider that the voltage distribution at the test object is not influenced by the surroundings. Here, the operation of the generator shall not be disturbed by undesirable discharges or even breakdowns.

Note The strong polarity effect is typical for streamer discharges in air. There is no remarkable polarity effect for internal insulation. If internal insulation, e.g. of a power transformer, shall be tested with LI voltage, a flashover of the air-part of the bushing is avoided when the test is performed at negative LI voltage.

At SI voltages, a combination of streamer and leader discharges determines the breakdown voltage between the generator and the surroundings. The electrodes of the HV components of the test system shall be designed in such a way that no leader discharge appears, this means with larger radii (Fig. 7.15c). The effect of enlargement of the distance to the surrounding is very week because of the low leader gradient (about 1 kV/cm). Therefore, it is recommended to optimize the electrodes of the HV components by a field calculation with the realistic conditions of the test room. As a rough hint, the distance must be in minimum 20% larger than for LI voltage, and the surface field strength of the electrodes at SI voltage should be below 20 kV/cm.

When a generator and related HV components are used for LI and SI voltage generation, the electrodes are determined by the maximum SI test voltages, even when they are about 25% lower than the maximum LI test voltages. An optimum utilization of a test area can be reached when a generator is moveable in the laboratory, e.g. by air cushions. The design principles for outdoor generators (Fig. 7.15d) are identical. They require also large electrodes for SI voltage generation, but under rainy conditions, the maximum output voltages must be remarkably reduced.

- 1.

Manual operation with measurement and evaluation of LI/SI parameters: The operator has to control the test system including adjustment of the voltages and duration of the breaks between impulses, and the evaluation and presentation of the test result (test record). The charging and triggering process must be controlled. When control and measuring components are not connected to one system, this has to be done by the operator. This traditional mode is very seldom applied for industrial testing and research work, but applied for e.g. student’s training.

- 2.

Computer-supported operation and test result presentation: The test is performed manually, but the precise adjustment of test voltages—this means that of the distance of the switching gap as well as that of the charging DC voltage—and the test data presentation are overtaken by the system. Control and measuring components are connected. This mode is applied for larger and expensive test objects in industrial testing and for research work.

- 3.

Automatic testing according to a pre-given test procedure by a computer control: The PC software for the test procedure is configured by the operator before, the HV test itself is performed, evaluated and presented automatically. Intervention of the operator is not necessary, but the test can be interrupted or terminated at any time by the operator. This mode is applicable for testing of very similar or even identical test objects in a larger scale or for statistical investigations in research work.

The control system delivers the commands for switching the breakers on and off, for adjusting the switching gaps of the generator for the pre-selected voltage and for the appropriate charging voltage adjusted by a thyristor controller. Based on the voltage measurement, the computer control checks that the voltage values are within the pre-given sequence and tolerances. Based on the evaluation of the voltage shape, breakdowns are recorded for the evaluation of the test. Also the evaluation of the related currents might indicate whether a test has been successful or has failed. The style of the test record depends fully from the intention of the user.

Switching cubicle and DC rectifier unit : A LI/SI test system has a relatively low power demand of some 10 kW. The switching cubicle contains the power switch and the operation switch, the instrument transformers for supply voltage and current measurement and protective equipment. The built-in thyristor controller enables a constant-charging current output of the connected rectifier unit. This DC rectifier unit is usually a doubler circuit (see Sect. 6.1.2 and Fig. 6.3) or for symmetric charging, a half-wave rectifier with symmetric output (modification of Fig. 6.2). Depending on the rated power and energy of the impulse generator, the charging voltage corresponds to the stage voltages (100–200 kV) and the charging currents are between few 10 mA and some 100 mA. The duration of the charging which determines the impulse voltage repetition rate depends on the total energy of the generator and is usually between 10 and 60 s. For special application, also faster charging processes and higher repetition rates can be realized.

7.1.3 Circuits for Oscillating Impulse Voltages

Oscillating lightning impulse voltages (OLI). a OLI test voltages. b Equivalent circuit for oscillating impulse voltage generation. c 900 kV impulse test system for 850 kV LI and 1600 kV OLI voltages.

Courtesy of Siemens Berlin

and

and  (Eq. 7.5). The total load Cl = Clb + Clt is the sum of the basic load and the test object load. The fixed series inductance Ls replaces the front (damping) resistors. According to IEC 60060-3:2006, impulse voltages with oscillations f0 > 15 kHz are considered as “oscillating lightning impulse (OLI) voltages”

(Fig. 7.16a), such with f0 < 15 kHz as “oscillating switching impulse (OSI) voltages”

(Fig. 7.17a). The damping is determined by the losses in the circuit, for pure capacitive test objects mainly by the tail resistors Rt of the aperiodic impulse. As these are higher for OSI than for OLI voltages, OSI voltages show not only a lower frequency, but also a larger damping (Fig. 7.17a).

(Eq. 7.5). The total load Cl = Clb + Clt is the sum of the basic load and the test object load. The fixed series inductance Ls replaces the front (damping) resistors. According to IEC 60060-3:2006, impulse voltages with oscillations f0 > 15 kHz are considered as “oscillating lightning impulse (OLI) voltages”

(Fig. 7.16a), such with f0 < 15 kHz as “oscillating switching impulse (OSI) voltages”

(Fig. 7.17a). The damping is determined by the losses in the circuit, for pure capacitive test objects mainly by the tail resistors Rt of the aperiodic impulse. As these are higher for OSI than for OLI voltages, OSI voltages show not only a lower frequency, but also a larger damping (Fig. 7.17a).

Oscillating switching impulse voltages (OSI). a OSI test voltages. b 1200 kV impulse test for 900 kV SI and 1600 kV OSI voltages

OLI characteristic of an impulse voltage test system (250 kV/5 kJ)

When the generator has to be designed for a maximum cumulative charging voltage V0Σmax, the basic load capacitance and also the series inductance must be able to withstand the maximum oscillating impulse voltage which is much higher than the V0Σmax (Eq. 7.7). The insulation design of the basic load capacitance for OLI and OSI voltages is practically identical, whereas that of the series inductance is very different (compare Figs. 7.16c with 7.17b). For OLI voltages, a low inductance is required which can be made easily. Contrary to that the OSI generation requires a much higher inductance. Now, stray capacitances must be taken into consideration which would cause a non-linear voltage distribution along the coil. To avoid that, a longitudinal voltage control by toroid electrodes is necessary. The coil for OSI voltage is much longer, thicker and heavier than the one for OLI voltage. Furthermore, it has been found that the benefit of OSI testing is low; therefore, mainly OLI testing is applied (see Sect. 10.3.1).

It should be mentioned that also bipolar oscillating impulse voltages can be generated based on impulse voltage circuits (Schuler and Liptak 1980). They arranged the inductance in parallel to the load capacitance and applied the bipolar OLI voltage for testing of rotating machines.

Damped alternating (DAC) voltage. a A full DAC impulse (including the DC ramp for charging). b The short oscillating part of the DAC impulse. c A sequence of DAC impulses as occasionally used for withstand tests

7.1.4 OSI Test Voltage Generation by Transformers

Generation of unipolar OSI voltages by transformers (Schrader et al. 1989). a Schematic circuit diagram. b Equivalent circuit. c Unipolar OSI voltage

The output (Fig. 7.20c) is a unipolar OSI voltage with frequencies of 100 up to 1000 Hz; this means with time-to-peak Tp > 500 μs.

Generation of bipolar OSI voltages by transformers (Schrader et al. 1989). a Schematic circuit diagram. b Equivalent circuit. c Bipolar OSI voltage

Feeding modes of a three-stage cascade transformer for OSI voltage generation. a Single feeding into the primary winding of the lowest transformer. b Single feeding into the tertiary winding of the middle transformer. c Triple feeding into the tertiary winding of each transformer

3-MV transformer cascade with OSI attachment and triple feeding mode

7.1.5 Circuits for Very Fast Front (VFF) Impulse Voltages and Solid-State Generators

Time characteristic of a VFF voltage

Generation of VFF test voltages. a Equivalent circuit. b Potential diagram

Principle circuit for VFF investigation of gas insulation

Solid state generators : For low output voltages and special applications, the progress of power electronics enables the development of impulse generators based on solid state elements instead of switching gaps [e.g. Shi et al. (2015), Elserougi et al. (2015), Kluge et al. (2015)]. They can also be recommended for HV testing e.g. of low voltage equipment (IEC 61180). This trend should deserve attention, even if it is not yet applicable for testing of high- and medium-voltage equipment.

7.2 Requirements to LI/SI Test Systems and Selection of Impulse Voltage Test Systems

The preceding subsections have shown that a wide variety of impulse voltage shapes can be generated. For research work, development and even diagnostic testing, this variety can be used. But for quality testing, impulse voltages shall be applied which represent external (lightning) and internal (switching) over-voltages being reproducible within certain tolerances. Requirements for these test voltages are given in standards like IEC 60060-1:2010 or IEEE Std. 4 (Draft 2013) and will be explained in the following.

7.2.1 LI Test Voltage and the Phenomenon of Over-Shoot

7.2.1.1 Requirements of IEC 60060-1 and IEEE Std. 4 to Standard LI Voltages 1.2/50

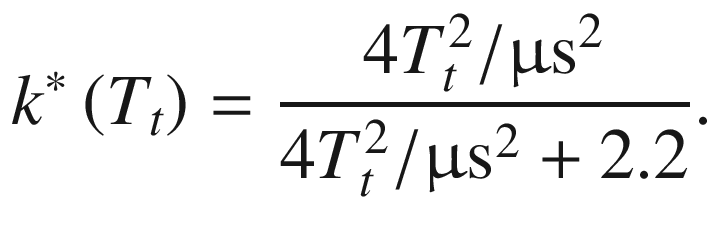

Test voltage functions a According to IEC 60060-1:2010 with empirical data and limit value of IEC 60060-1:1989. b Comparison with proposal of CIGRE WG D1.36 (2017) for UHV LI tests

Determination and presentation of the test voltage curve. a Recorded curve, base curve and residual curve. b Test voltage function. c Base curve, filtered residual curve and test voltage curve. d Presentation of test voltage curve and recorded curve

- 1.

Determine the base curve Vb(t) as an estimate of the exponential function with the parameters V0, τ1 and τ2:

(7.11)

(7.11)The base curve (Eq. 7.11) represents the recorded curve without over-shoot and shall be characterized by its peak value VB, whereas the full recorded curve is characterized by its extreme value VE (Fig. 7.28a).

- 2.

Find the residual curve as the difference between the recorded curve and the base curve (Fig. 7.28a):

(7.12)

(7.12) - 3.

Use a digital filter with a transfer function (amplitude–frequency response) equal to the test voltage function H(f) = k(f) (7.10a, b, as described in detail in IEC 60060-1:2010, Annexes B and C) and use it for filtering the frequency spectrum VR(F) of the residual curve. The result is the filtered residual curve in the frequency domain

and—after re-transformation to the time domain—the filtered residual curve VRF(t) (Fig. 7.28b). (7.13)

(7.13) - 4.

Superimpose the filtered residual curve on the base curve to get the test voltage curve (Fig. 7.28c):

(7.14)

(7.14) - 5.

In a presentation of the result, both—the recorded curve and the test voltage curve—shall be shown (Fig. 7.28d).

Note It should be mentioned that the handling of the zero-level problem is not considered here. For the zero level and the details of the implementing the evaluation software, see IEC 60060-1:2010, Annexes B and C and IEC 61083-2:2013, see for the filter curve also Lewin et al. (2008).

It should be mentioned that in addition to the computer-aided evaluation, also a manual calculation of the test voltage value VT is described in IEC 60060-1:2010 (Annex B.4) as well as by Berlijn et al. (2007). This procedure considers not the whole frequency spectrum of the residual curve, rather its corresponding value k(fos) at the single main frequency fos of the over-shoot which is simply multiplied with the maximum of the residual voltage VRmax(t). The result is superimposed on the estimated base curve to get the test voltage value VT. In contrast, the filtering (Eq. 7.13) works also when the over-shoot is the result of a mixture of frequencies and when noise signals of higher frequencies are superimposed on the recorded curve. The manual evaluation cannot be recommended.

In case of a smooth recorded curve (Eq. 7.11) with VE = VB, one gets VR(t) = VRF(t) = 0 because of k(f) = 1. IEC 60060-1:2010 requires that all parameters of the LI test voltage are evaluated from the test voltage curve. When an LI test voltage fulfils the following requirements, it is a standard LI test voltage 1.2/50:

Parameter definition for full LI test voltages

Note For test objects of high capacitance as cables or capacitors, the upper tolerance limit might be significantly enlarged to 5 μs or even more. Also for UHV equipment, an upper tolerance limit in the order of 2.5 μs is under discussion.

The time-to-half-value T2 is a virtual parameter as the time interval between the virtual origin which is the intersection between the time axis and the straight line drawn through the points A and B in Fig. 7.29, and the instant when the voltage crosses the half of the test voltage value (Fig. 7.29): It is required T2 = 50 μs with a tolerance of ±20%, this means the real value has to be within (40–60) μs.

The latest edition of IEEE Std. 4 (2013) recommends an over-shoot up to 5%, but allows an increase to 10% for reasons “to allow waveforms accepted by the historical” smooth curve of the “over-shoot method” (IEEE Std. 4—1995 and IEC 60060-1:1989).

Quality tests require in addition to full LI test voltages also chopped LI test voltages (LIC) which represent the stress of the insulation after a protecting device (e.g. an arrester or a protection gap) has operated. An LIC voltage is also caused by any breakdown in the HV circuit, but in the following, only controlled breakdowns with a chopping gap will be considered (see Sect. 7.1.2.4).

Chopped lightning impulse voltages. a Front-chopped LIC voltage. b Tail-chopped LIC voltage. c Linearly rising front-chopped impulse

Note According to the IEC opinion, a front-chopped LIC voltage is not required for testing objects with windings, because the tail-chopped LIC voltage causes a higher steepness and consequently a more non-uniform voltage distribution in the test object. The traditional IEEE opinion considers more the representation of high over-voltages limited by protection devices. It seems that in a future version of IEEE Std. 4, the IEC practice will be applied, too.

The voltage increase is considered to be approximately linear from 30% up to the instant of chopping. The tolerance of the steepness is characterized by a band of ±0.05 · T1 from the mean line through AB (Fig. 7.30c). The parameters of linearly rising LIC voltages are not specified in the horizontal standards, but in the relevant apparatus standards.

Voltage value : The evaluation of tail-chopped LIC voltages can be made with a method adapted to the k-factor calculation. For this, two records are needed, one of the tail-chopped LIC voltage from the performed test and one full reference LI voltage on lower voltage without changing the set-up of the HV test circuit (except of the switching gaps and the charging voltage of the generator) and the measuring system. The reference LI curve is used for the determination of the base curve. The recorded LIC curve is treated with that base curve similar as described above. For more details, see IEC 60060-1:2010 (Annex B.5). The problem of over-shoot does not appear for front-chopped impulses, they can be evaluated as shown in Fig. 7.30a.

7.2.1.2 Situation and Future of the Treatment of Over-Shoot

The evaluation method according to the IEC and IEEE standards as described above is an important first step into the direction of a physically correct evaluation of LI test voltages with overshoot, but it is also a compromise between new ideas and traditional thinking. Therefore, it shall be tried to explain in the following the possible directions of the further improvement of the k-factor method. Let us consider the new evaluation method in comparison with that of IEC 60-1:1989 (Fig. 7.27).

As considered in Sect. 7.1.2.3, the inductance and capacitances in the circuit may cause oscillations which are damped by the resistive losses in the circuit. The oscillations have remarkable influence on the breakdown behaviour when they appear in the region of the peak and increase the peak value of the LI test voltage. In case of a strong damping, the oscillation is reduced to a single half-wave, which is called “over-shoot”. In the following, the term “over-shoot” shall also include oscillations of lower damping.

A clear decrease in the test voltage factor with increasing frequency has been found (Fig. 7.27, measuring points), but the dispersion of the results was so large, that no clear influence of the different types of insulations has been identified. Therefore, a common k-factor curve has been evaluated (Fig. 7.27 and Eq. 7.10a, b), which is overtaken into the standards (see Sect. 7.1.2.1).

Differences of LI parameter evaluation according to IEC 60060-1:2010 and IEC 60-1:1989

Parameter | Over-shoot frequency f < 0.5 MHz | Over-shoot frequency f > 0.5 MHz |

|---|---|---|

Test voltage value | 0…−3% | +2%…+6% |

(V2010 − V1989)/V1989 | ||

Front time | 0…−6% | 0…+15% |

(T1 2010 − T1 1989)/T1 1989 | ||

Time to half-value | 0…+5% | −4%…7% |

(T2 2010 −T2 1989)/T2 1989 | ||

Over-shoot | Independent on the frequency | |

(ß2010 − ß1989)/ß1989 | −10%…+40% | |

Definition of over-shoot in conjunction with the formative time model. a Example for an aperiodic over-shoot using a percentage of extreme value VE. b Example for oscillating over-shoot using 0.9 · VE. c Example for oscillating over-shoot using the test voltage value VT

A limitation of ß° would mean a limitation of the formative voltage–time area which considers the really acting stress combination of voltage and time.

Test voltage function depending on over-shoot duration (Eq. 7.21)

Expected modifications of the test voltage function

It can be assumed that different characteristics will be found for different electric fields, different insulation materials and possibly even for different over-shoot magnitudes. Also the evaluation algorithms and the remarkable uncertainty of the determination of the test voltage function (Okabe et al. 2015) must be taken into consideration. Possibly for a future standard IEC 60060-1, all available experimental results should be used to find one common test voltage function applicable within acceptable tolerances for parameter evaluations of all insulations.

The fitting method for extracting the base curve as described above (Eq. 7.11) is also subject of ongoing investigation, (e.g. Satish and Gururaj 2001; Kuan and Chen 2006; Ueta et al. 2011a, b, c, d, 2012a, b; Garnacho et al. 2013; Pattanadesh and Yutthagowith 2015). The introduction of a new evaluation method for the base curve could cause differences in the LI parameter evaluation. Contrary to the test voltage function, there seems to be no urgent need for the introduction of a new method for the determination of the mean curve. First, it must be shown that the present method is insufficient for practical cases.

Related to testing of UHV equipment , the CIGRE Working Group D1.36 (2017) has summarized the present knowledge: It has been shown that for UHV test objects the requirements T1 ≤ 1.56 µs and ß ≤ 10% cannot be met, when the capacitance of the test objects reaches the order of 10 nF (see also the following Sect. 7.2.1.3). It is recommended to increase the upper tolerance limit to T1 = 2.5 µs and the acceptable overshoot to ß ≤ 15% when testing UHV equipment with Vm > 800 kV. Furthermore the test voltage function for UHV LI testing is changed (Fig. 7.27b) to the above mentioned Eq. (7.10b) and an improved procedure for the base curve estimation is proposed. Hopefully IEC TC42 will provide on that basis the next edition of IEC 60060-1.

Last but not least, there are discussions to reduce the over-shoot in LI testing by the over-shoot compensation (see Sect. 7.1.2.3).

7.2.1.3 Interaction Between HVLI Test System and Test Object

Most test objects—like insulators, bushings, GIS, power transformers or cable samples—provide a capacitive load for the test system. In few cases, test objects have an inductive characteristic, like the low-voltage winding of power transformers. Resistive test objects do not play any role, because outdoor insulations are not tested under wet or polluted conditions with LI voltages. The influence of the test object shall be explained by the equivalent single-stage circuit (Fig. 7.4).

Influence of the load capacitance on selection of front and tail resistors of a generator 2000 kV/400 kJ of ten stages. a Principle of the selection of front resistance. b Situation of the tail resistance (Kind and Feser 1999)

for T1 ≤ 1.56 µs can roughly be estimated from the total capacitive load (in µF) (Cl = Cb + Cto) and the total circuit inductance (in µH) (Ls = Lgenerator + LHV lead + Ltest object + Lcurrent return) by

for T1 ≤ 1.56 µs can roughly be estimated from the total capacitive load (in µF) (Cl = Cb + Cto) and the total circuit inductance (in µH) (Ls = Lgenerator + LHV lead + Ltest object + Lcurrent return) by

With the characteristic UHV load capacitances (up to more than 10 µF) it might be difficult to meet the limit of the overshoot β ≤ 10%. Therefore the test standards for UHV equipment (now under preparation) shall allow a higher LI overshoot (up to β = 15%) and/or longer LI front time (higher front resistors) for sufficient attenuation of the overshoot.

Selection of front resistance depending on test object capacitance

The time to half-value T2 (characterized by τt, Eq. 7.22b) is not strongly influenced by the test object capacitance because it is dominated by the impulse capacitance Ci (Fig. 7.35b). One tail resistance is sufficient to cover the whole tolerance band of the time to half-value between 40 and 60 μs.

The circuit efficiency factor can easily be estimated by Eq. 7.23. The generator with its basic load reaches usually a total efficiency factor η ≈ 0.95 for Ci ≫ Cto. It decreases slightly with increasing test object capacitance and values Cto > 0.2 Ci cannot be recommended.

Testing of objects with inductances. a Equivalent circuit. b Equivalent circuit with “Glanninger” attachment. c Comparison of the impulse shape

7.2.2 SI Test Voltages

7.2.2.1 Requirements of IEC 60060-1 and IEEE Std. 4

Recorded curves of SI test voltages 250/2500 and their reproducibility for different peak values

When an SI voltage fulfils the following requirements, it is a standard SI test voltage:

The test voltage value Vt is the maximum value of the recorded voltage curve (Fig. 5.39). In a SI voltage test, the required test voltage value must be adjusted with a tolerance of ±3%.

Definitions of SI test voltages. a Standard impulse 250/2500. b SI testing of equipment with saturation effects

Note When SI testing was introduced in the late 1960s, the evaluation of the time-to-peak has been made according to all appearances. This principle has not been suitable for computer evaluation, and therefore, the evaluation based on the intersection has been introduced with IEC 60060-1:2010.

The definition front time—which would be in the order of T1 ≈ 170 μs—has not been introduced because the equivalent time-to-peak of Tp = 250 μs is used for decades, and for traditional reasons it should not be changed.

As shown by Sato et al. (2015) Eq. (7.25) is only valid for standard SI voltages, its application to non-standard SI voltages (e.g. 20/4000 µs as accepted for SI voltage tests on site, see Sect. 10.2.1.3) might lead to failures up to 25%. Sato et al. give an formula better adapted to the full range of SI voltages.

Note The tremendous tolerance of T2 is related to tests on equipment with saturation phenomena, e.g. caused by the iron cores of transformers and reactors. There the SI voltages cause a saturation of the magnetic core which leads to the immediate collapse of the voltage (Fig. 5.39b). For such tests additional parameters, the time above 90% and the time to zero have been introduced (see below). The wide tolerance interval is acceptable because the breakdown process in air—development of leader discharges (see Fig. 7.3)—is determined by the steepness of the front of the SI voltage and very few by development of its tail.

The time above 90% T90 is the interval during which the SI voltage exceeds 90% of its maximum value (Fig. 7.39b).

The time to zero TZ is the interval between the true origin and the instant when the SI voltage has its passage through zero (Fig. 7.39b).

The parameters shall not been mixed up, because a standard SI test voltage 250/2500 has to be characterized by the set (Vt; Tp; T2) and for testing equipment with saturation effects the different SI set (Vt; Tp; T90; TZ) may be used.

7.2.2.2 Interaction Between HVSI Test System and Test Object

Consideration of polarity effects : Both, LI and SI voltage tests on internal insulation shall be performed at negative polarity to avoid flashovers at bushings or terminations in air. Whereas non-uniform air insulations have much lower breakdown voltages at positive polarity, there is approximately no, sometimes even a slight opposite polarity effect for internal insulation. Also the design of the control electrodes and of the insulation structures of the HV components of an LI/SI test system is determined by the maximum positive SI voltage to be generated. Positive specific SI breakdown voltages of non-uniform fields in air can go down to the order of 1 kV/cm, whereas at LI voltage one can assume a value of 5 kV/cm.

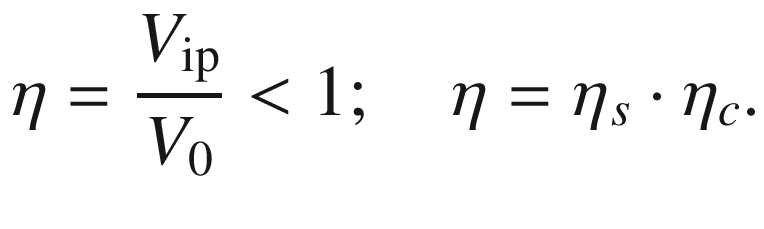

Capacitive test objects : It has been shown in Sect. 7.1.2 that the efficiency factor can be understood as the product of the shape efficiency and the circuit efficiency (Eq. 7.1). The shape efficiency factor ηs of SI voltage is much lower than of LI voltage. The circuit efficiency factor ηc can be estimated according to Eq. 7.24 as for LI voltages. For a load capacitance Cl = Cb + Cto = 0.2 · Ci, the circuit efficiency becomes ηc = 0.83. With a shape efficiency of ηs = 0.75 one gets a total efficiency factor of only η = 0.62 (Eq. 7.3). The time-to-peak is less sensitive to changes of the load capacitance than the front time of LI voltage. The tolerance of the time to half-value is so large that changes of the test object do not play any role for the selection of the tail resistors. When an LI/SI test system is ordered the maximum expected test object capacitance must taken into consideration for the selection of the impulse energy per stage (Eq. 7.3).

Resistive test objects : Wet and pollution tests of external insulation are also performed at SI test voltages, especially for EHV and UHV equipment. The influence of the resistance of a polluted test object to the total front resistance of an SI generator (up to some 10 k′ Ω) remains negligible. But during testing heavy discharges with currents of some Amperes may cause remarkable voltage drops. This is not only a problem for wet and pollution tests, but also when long air gaps with leader discharges are investigated. As described above for AC and DC voltage, the voltage drop can be calculated when the height and duration of the current pulse are known or assumed. Impulse currents of peak values above 10 A and duration of some 10 μs have been observed (Les Renardieres Group 1977). There is not yet any standard on the acceptable voltage drop at a pre-given current impulse. In any case for the mentioned tests, an impulse generator of high impulse energy should be applied.

Inductive test objects with saturation effects: For testing power transformers, the IEC 60076-3:2013 requires Tp > 100 μs; T90 > 200 μs and TZ > 1000 μs. For the prolongation of the time to zero, a pre-magnetization of the core with SI voltage of opposite polarity and lower maximum value (Ve > 0.7 · Vt) can be performed if necessary. Also after a SI voltage test, the core should be demagnetized by applying lower SI voltages of opposite polarity.

7.3 Procedures and Evaluation of LI/SI Voltage Tests

Breakdown and standardized withstand voltage tests as well as the statistical background are already described in Sect. 2.4. The following explanations are related to special LI/SI test procedures and refer to that section.

7.3.1 Breakdown Voltage Tests for Research and Development

The multiple-level method (MLM) is the most important and mainly used test method for the determination of the performance function of insulation samples (see Sect. 2.4.3 and Fig. 2.31). The performance function describes the relationship between stressing LI/SI voltages and breakdown probabilities completely. The MLM test can be easily performed on self-restoring insulation in air. The independence might be checked by independence tests. A procedure for that test is explained in Table 2.8. Usually the test results for air gaps are independent when the break between two LI/SI voltages is not shorter than several seconds.

For air or SF6 insulation with surfaces to solid insulation (e.g. insulators), before the further evaluation of the test, a check of independence is more important than for gases alone. If dependence is indicated, the test procedure should be modified, e.g. by longer breaks between two impulses following each other. Also the short application of a lower impulse voltage of opposite polarity or of a low AC voltage during the break may help to get independent results.

For liquid impregnated and solid insulation the MLM application requires for each LI/SI voltage stress a new test sample. This is a remarkable effort and the limited reproducibility of the test samples causes an additional contribution to the dispersion of the measured performance function. For such test objects it can be checked to apply the progressive stress method (PSM; Fig. 2.26c). where one sample is applied to a series of impulses until breakdown. A single test sample delivers more information in a PSM test than in a MLM test.

Performance function of an air gap evaluated by the maximum-likelihood method based on a normal (Gauss) distribution

When instead of the whole performance function, the estimation of a certain quantile (e.g. V50 or V10) is sufficient, the up-and-down method can be applied (Sect. 2.4.4 and Figs. 2.38 and 2.39). Also for that test procedure a maximum-likelihood evaluation is possible and can be recommended.

7.3.2 LI/SI Quality Acceptance Tests

A passed quality acceptance LI/SI test verifies the insulation coordination (Sect. 1.2) by performing the test according to a standardized procedure, see Sect. 2.4.6; Fig. 2.43 and IEC 60060-1:2010.

- A1.

The LI/SI test voltage is lower than the 10%—breakdown voltage: Vt < V10.

- A2.

The LI/SI test voltage is 15-times applied and the number of breakdowns is k ≤ 2.

- B.

The LI/SI test voltage is three times applied and no breakdown may occur (k = 0).

For insulation as that of a GIS consisting of a self-restoring (SF6 gas) and a non-self-restoring (solid insulators) part, it has to be shown that the breakdown had happened in the self-restoring part. This can be indicated by a certain number of withstands at the LI/SI test voltage after the breakdown. A further indication can be a PD measurement which shows no increased PD level. The valid procedure is specified by the relevant apparatus committee of IEC or IEEE. In the following some examples for LI/SI acceptance test procedures are given:

Testing of external insulation (IEC 60071-1): The procedure A1 (Vt < V10) requires the estimation of V10 from a performance function measured down to this low breakdown probability or for known V50 and standard deviation σ from V10 = V50–1.7 σ or from an up-and-down test with seven impulses per voltage level (see Sect. 2.4.4). The procedure A2 (n = 15/k = 2) is applicable for all other cases when the above necessary parameters are not available and the effort for their determination is assumed to be too high. It is necessary to mention that the LI voltage tests are applied to dry insulation (see Sect. 2.1.2), whereas the SI voltage tests are applied to wet insulation (see Sect. 2.1.3).

Note It is important to state that the “horizontal” IEC 60071-1:1993 requires only three impulse voltages and in case of one breakdown nine additional voltage impulses during which no disruptive discharge is tolerated. This procedure is of higher uncertainty, and therefore, it had not been considered as sufficient when the “vertical” GIS standard was established in 2003.

- V m

rated phase-to-phase voltage in Volts;

- f

rated frequency in Hertz;

- Z

short-circuit impedance in % related to the test terminals;

- S r

three-phase power rating in Volt-Amperes;

- V t

LI test voltage value in Volts;

- T 2

time to half-value of he LI voltage in μs;

- η

efficiency factor in per unit.

The LI voltage test is a routine test for power transformers Vm > 72.5 kV, for lower rated voltages a type test. For transformers Vm > 170 kV, the test includes also chopped LI voltages (LIC). An SI voltage test is a routine test for transformers Vm > 170 kV and for lower rated voltage a special test. The impulse shall be of standard shape 1.2/50 within the usual tolerances. The evaluation according to the k-factor method is allowed, but alternatively IEC 60076-3:2013 defines some strange differences to IEC 60060-1:2010:

one full LI reference voltage of (0.5–0.6) · Vt,

one full LI test voltage Vt,

two chopped (LIC) test voltages of 1.1 Vt,

two full LI test voltages Vt.

one SI reference voltage (0.5–0.7) Vt and

three SI test voltages Vt.

Both tests are successful if no internal breakdown collapses the voltage. For the LI test, additionally, the normalized voltage shapes of the reference LI voltage and of the LI test voltage, as well as the normalized shapes of the measured impulse currents (see Sect. 7.5) at the two voltage levels should be identical.

LI/ SI testing of cables (IEC 62067:2006): The routine test of cables does not include an LI/SI test voltage. The AC withstand test and a sensitive PD measurement are considered to be sufficient for verifying a correct production, but in defined intervals, more detailed cable sample tests (which repeat parts of the type test) are performed to confirm the correct production.

A cable type test includes a long set of single tests including LI/SI tests which are performed at warm cable samples after a heating cycle voltage test, which includes 20 single cycles of one day each, and a PD measurement. First, the SI test is performed with 10 positive and 10 negative SI voltages. If no breakdown occurs, the sample has passed and can be stressed with LI voltages according to the same procedure. The PD test is repeated after the LI/SI test.

Additionally, there are pre-qualification tests on complete cable systems of about 100 m length with joints and terminations. The total test duration is about one year with in minimum 180 heating cycles. The LI test voltage shall be applied to the whole test assembly or to samples with a length of in minimum 30 m after each heating cycle. The test temperature shall be in an interval between maximum conductor temperature and 5 K above. The test consists of 10 positive and 10 negative LI voltage applications again. It is passed if no breakdown occurs.

As the capacitances of the cable samples are between 0.15 and 0.3 nF/m, the test object capacitance for 30 m samples may reach 9 nF and for 100 m up to 30 nF. These are quite high capacitances, and therefore, the standard allows front times T1 = 1…5 μs, T2 is within the standard values T2 = 40…60 μs. For SI test voltages, the usual tolerances shall be applied.

7.4 Measurement of LI and SI Test Voltages

To measure the peak value of high impulse voltages, originally sphere gaps have been employed, as already presented in Sect. 2.3.5. However, this direct measurement method is nowadays only recommended for performance checks including linearity tests. Occasionally, also field probes are applicable, as described in Sect. 2.3.6, particularly for measuring very fast transient voltages characterized by time parameters down to the nanosecond range (Feser and Pfaff 1984). This Section is addressed to indirect measuring methods using a HV converting device, which is connected to the LV measuring device via a transmission system, such as a BNC cable or even a fiber optic link. As the design of the converting device is the most challenging task, the following treatment focuses mainly on this issue. More details on this subject can also be found in the textbook of Schon published in 2013.

7.4.1 Dynamic Behaviour of Voltage Dividers

Set-up for measuring the step voltage response of LI voltage dividers

Usually, a step voltage of some 100 V in magnitude and a rise time in the nanosecond range is applied. To accomplish such a short rise time commonly a mercury-wetted relay is used, which is often referred to as Reed-Relay. If switching at repetition rate around 100 Hz, disturbing background noises can effectively be rejected by the so-called averaging mode. Due to the proximity effect, it has to be taken care that the voltage divider is arranged in agreement with real HV test conditions where neither the HV connection lead nor the measuring cable should be replaced after the performance test has been carried out.

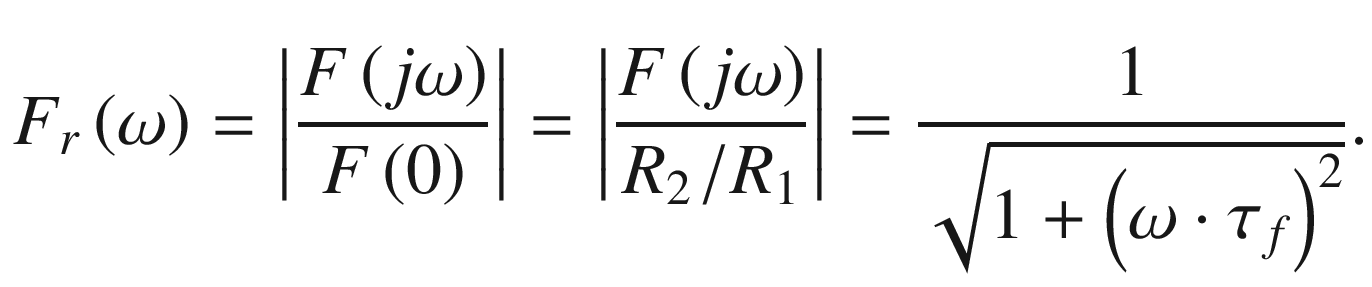

Equivalent circuits of unshielded resistive voltage dividers. a Distributed capacitances (transmission line). b Lumped capacitance connected to the HV arm. c Lumped capacitance integrated in the LV arm (low-pass filter) with Rs = R1 and Cp= Ce/6

In this context it should be noted that the network with distributed elements according to Fig. 7.42a can be replaced by an equivalent circuit, which contains only a single lumped capacitance, which is equal to 2/3 Ce, as illustrated in Fig. 7.42b. Even if this approach is commonly used in the relevant literature, it can further be simplified, as illustrated in Fig. 7.42c. Here, the series resistance of the low-pass filter is equal to the resistance R1 of the HV arm, while the parallel capacitance amounts 1/6 of the total earth capacitance Ce of the HV divider column, which can roughly be estimated using the so-called antenna formula, as will be discussed below more in detail.

Dynamic behavior of a low-pass filter of first order. a Amplitude–frequency response. b Unit-step response

Example Consider the HV arm of an LI divider of resistance R1 = 10 kΩ and stray capacitance of Ce = 30 pF, one gets the following values providing an equivalent low-pass filter of first order (Fig. 7.42c): Rs = R1 = 10 kΩ and Cp = Ce/6 = 5 pF. Based on this the following values of the circuit elements are obtained:

• Response time constant | τf = R1 · Ce/6 = 50 ns |

• Rise time | tr = 2.2 · τf = 110 ns |

• Upper limit frequency | f2 = 1/(2 · π · τf) = 3.2 MHz |

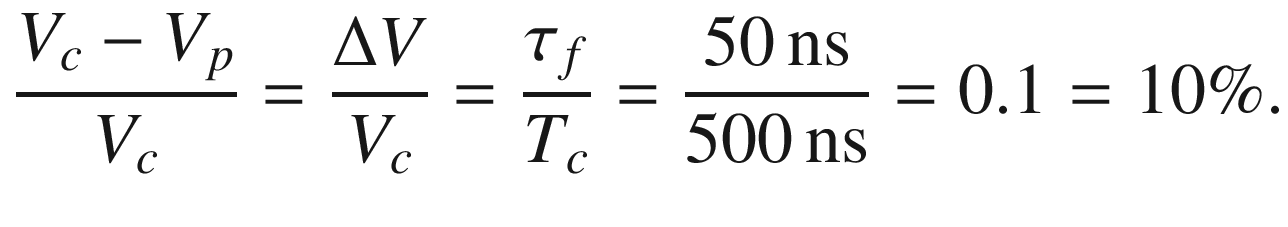

Voltage ramp v1(t) chopped at time Tc = 500 ns and output signal v2(t) after passing a low-pass filter of first order characterized by the time constant τf

Experimentally determined response (red curves) of a capacitive (a) and a resistive (b) divider subjected to a step voltage (blue trace)

![$$ \tau_{a} = \int\limits_{0}^{\infty } {\left\{ {1 - \left[ {g(t)} \right]} \right\}} {\text{d}}t = \tau_{f} . $$](../images/214133_2_En_7_Chapter/214133_2_En_7_Chapter_TeX_Equ36.png)

Unit-step response parameters of voltage dividers. a RC circuit (low-pass filter of first order). b RLC circuit

• Experimental response time | TN = Tα − Tβ + Tγ − Tδ + Tε |

• Partial response time | T α |

• Residual response time | TR = Tβ − Tγ + Tδ − Tε … |

• Over-shoot • Settling time • Origin of step response | β rs t s (definition see text below) O 1 (definition see text below) |

The unit-step response is usually recorded for a nominal epoch, which is defined as the range of values between the minimum (tmin) and the maximum (tmax) of the relevant time parameters of the impulse voltage for which the measuring system is to be approved, such as the front time T1 for full and tail-chopped LI voltages, the time to chopping Tc for front-chopped LI voltages, and the time to peak Tp for SI voltages. Moreover, the so-called reference level epoch has to be considered, which is defined as the time interval in which the reference level of the step response is determined with its lower limit being equal to 0.5 times of the lower limit of the nominal epoch (0.5 tmin) and its upper limit being equal to 2 times the upper limit of the nominal epoch (2 tmax). The above listed parameters are determined for the time span, which elapses between the origin O1 of the recorded unit step response and the settling time ts, with O1—the instant at which the recorded response curve starts a monotonic rise above the amplitude of the noise at the zero level of the unit step response, and ts—the shortest time for which the relative contribution of the residual response time becomes and remains less than 2% of ts, that means /TN – TR/ ≤ 0.02 ts, which must be satisfied for t > ts.

In the past, it was a common practice to estimate the measuring uncertainty of voltage dividers by the so-called convolution method, which is based on the characteristic unit-step response parameters. Results of international round robin tests revealed, however, that this method is not capable of determining the measuring uncertainty of technical HV impulse dividers within the limits specified in the relevant IEC standards. Among others (e.g. assumption of a low-pass filter) this is due to the fact that the origin of the recorded curve, which is denoted in IEC 60060-2010 as O1, appears more or less delayed if compared with that instant t = 0 when the voltage step is applied, see Fig. 7.45. This signal delay is mainly governed by the travelling wave velocity, which is in the order of 30 cm/ns for HV connection leads and the divider column as well, and almost 20 cm/ns for measuring cables. Moreover, disturbing oscillations could be excited (Fig. 7.45), for instance, due to reflections at the ends of the HV connection leads, or even caused by a poor design of the ground return leads. Consequently, the above mentioned origin O1 of the recorded response function cannot exactly be determined and leads thus inevitably to an erroneous determination of the characteristic response time parameters.

≤1% for the peak values of full LI and SI voltages as well as tail-chopped LI voltages

≤3% for the peak values of front-chopped LI voltages

≤5% for the time parameters of LI and SI voltages, in its range of use.

Response parameters recommended for LI and SI voltage reference measuring systems

Parameter | Full and tail-chopped LI voltages (ns) | Front-chopped LI voltages (ns) | SI voltages (μs) |

|---|---|---|---|

Experimental response time TN | ≤15 | ≤10 | |

Partial response time Tα | ≤30 | ≤20 | |

Settling time ts | ≤200 | ≤150 | ≤10 |

Due to the fact that the measuring uncertainty of a HV measuring system is mainly governed by the voltage divider itself, the above recommendations can in principle also be adopted for reference voltage dividers alone either to be approved by a National Metrology Institute or even by a Calibration Laboratory accredited by the National Institute of Metrology.

7.4.2 Design of Voltage Dividers

Arrangement of a measuring system for LI test voltages

7.4.2.1 Resistive Voltage Dividers

Example Consider a HV divider column of h = 4 m in high and d = 0.1 m in diameter. Inserting these values in Eq. (7.35), the earth capacitance attains Ce ≈ 58 pF. Provided, the resistance of the HV arm amounts R1 = 10 kΩ, one gets the following characteristic time constant of the equivalent circuit according Fig. 7.42: τf = R1 · Ce/6 ≈ 100 ns. Measuring a LIC voltage chopped at instant Tc = 0.5 μs, the measured peak value would be about 20% lower than the true value applied to the test object, see Fig. 7.44. Consequently, the here investigated voltage divider is not capable of measuring front-chopped LI voltages in compliance with in IEC 60060-2.

Photograph of a shielded resistive 2.2-MV LI voltage divider (Courtesy of TU Dresden)

Principle of the compensation of the partial currents between divider column and earth by the currents between HV electrode and divider column

Distribution of equipotential lines along the HV column of resistive LI voltage dividers. a Without field grading. b With field grading using a large shielding electrode

Based on practical experiences it can be stated that shielded resistive dividers having a HV resistance in the order of 10 kΩ are the only one applicable for measuring front-chopped LI voltages in compliance with IEC 60060-2:2010 up to about 2 MV. For measuring higher LI voltages, the tall dividers must be equipped with excessively large and thus expensive shielding electrodes, which would reduce the mechanical stability. A carefully adapted shielding and potential grading is also limited under practical conditions due to the fact that the clearance to grounded and even energized structures must be chosen as large as possible to avoid any disturbances of the optimized field grading.

To improve the dynamic behavior, in principle the resistance of the HV arm could also be reduced significantly below 10 kΩ. However, this would substantially decrease the tail time and even the output voltage of the LI generator. Moreover, it has to be taken into account that the power dissipation in the HV divider column increases with the square of the applied voltage, which leads to a serious temperature rise. Based on practical experience it can be stated that an experimental response time below 15 ns can only be achieved when the resistance of the HV arm is reduced to few kΩ. Such voltage dividers, however, are only applicable for measuring LI voltages below 500 kV.

7.4.2.2 Damped Capacitive Dividers

Step-pulse response of a capacitive divider without and with a damping resistor

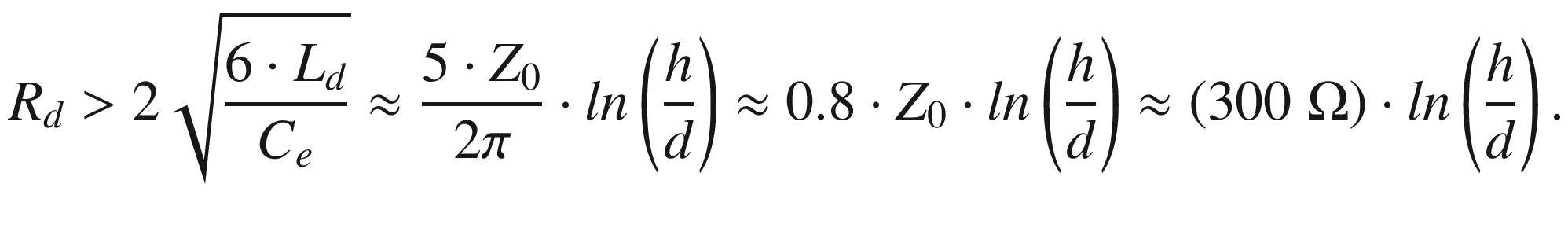

This is due to the fact that capacitive dividers act in the high-frequency range like an oscillating circuit, because under this condition the divider column composed of stacked capacitors can be simulated by a metallic cylinder and thus by an inductance, which interacts with the earth capacitances. To prevent such oscillations Zaengl (1964) and Spiegelberg (1964) proposed an interconnection of the stacked capacitors via serial resistors. The main benefit of this approach is not only that disturbing oscillations can drastically be attenuated, as exemplarily shown in Fig. 7.51b, but that the experimental response time constant can be reduced drastically, which is in contrast to the transfer characteristics of classical RC low-pass filters where the experimental response time constant increases proportional to the series resistance.

Equivalent circuit of a damped capacitive divider. a Damped C-divider with distributed elements. b Ideal R-divider connected to a RLC network

, it can also be written:

, it can also be written:

Example Consider a 2 MV divider which is composed of five stacked capacitors, where the total divider column shall be h = 5 m in high and d = 0.25 m in diameter, i.e. h/d = 20. Based on Eq. (7.40) one gets Rd > (300 Ω) · ln (20) ≈ 900 Ω. Thus the five stacked capacitors should be connected by four series resistors, each of (900 /4) Ω ≈ 225 Ω. Using an additional external resistor of 300 Ω, the total series resistance of the HV divider arm attains (900 + 300) Ω = 1,200 Ω. This has to be taken into account to choose the resistance to be integrated in the LV arm.

Example Applying Eq. (7.36) the effective inductance of the HV arm of the above considered 2 MV divider column of h = 5 m in high and d = 0.25 m in diameter gets L1 = 0.2 (µH/m) · 5 m · ln (20) ≈ 3 μH. Assuming, for instance, a divider ratio R2 /R1 = C1 /C2 = 1 /1000, the inductance L2 of the LV arm must be chosen as low as 3 nH.

LV arm of a damped capacitive divider comprising 60 parallel elements each composed of a resistor connected in series with a capacitor

Comparing the different divider types, it can be stated that damped capacitive dividers provide an excellent dynamic behaviour. Another benefit is that the power dissipating in the resistors inserted between the stacked capacitors is quite low due to the short duration of the transient current through the HV divider arm. Moreover, the effective capacitance of the HV arm provides a basic load for the LI generator. As the charging current is inversely proportional to the frequency, damped capacitive dividers are also well suited for measuring SI and AC voltages as well as composite voltages. If equipped with a high-ohmic resistor, which is connected in parallel to the HV arm, such an “universal” divider, as shown in Fig. 2.10, is also capable of measuring DC voltages including superimposed voltage ripples covering a frequency spectrum up to several kHz. Due to the wide field of application, the here presented damped capacitive divider is often also referred to as “multi-purpose divider”.

Section of a damped capacitive divider, rated voltage 200 kV

Experimental response time: TN ≈ 2 ns

Partial response time: Tα ≈ 5 ns

Settling time: ts ≈ 120 ns.

7.4.3 Digital Recorders

Recording and processing of LI test voltages (From the top: records of 50 and 100% test voltages; comparison of the normalized voltages; difference of the normalized voltages)

Photograph of a stand-alone digital recorder

Simplified block diagram of a digital recorder for HV measurements

The measuring uncertainty may be affected by both the hardware and the software. Due to the comparatively high quantization rate of nowadays available digital recorders, which attains usually 12 or 14 bits and even more, as well as the high sampling rate being in the order of 100 MS/s and above, the contribution of the hardware to the measuring uncertainty is much lower than that of voltage dividers. As the quantization error is given by 50% of the least significant bit

(LSB), this is approx. 0.012% for a slow-rising signal at quantization rate of 14 bit. However, the deviation from the true value increases significantly when front-chopped LI voltage according to Fig. 7.58 are measured at a sample rate of 100 MS/s. This is because the voltage difference  between each sample is inversely proportional to the sampling rate fs. For an assumed chopping time of, for instance, Tc = 0.5 μs and a crest voltage Vc, the voltage difference between each sample can be approximated by

between each sample is inversely proportional to the sampling rate fs. For an assumed chopping time of, for instance, Tc = 0.5 μs and a crest voltage Vc, the voltage difference between each sample can be approximated by  Under this condition the maximum deviation of the measured value from the true value, which is given by 0.5 LSB, attains 1% of the crest value Vc.

Under this condition the maximum deviation of the measured value from the true value, which is given by 0.5 LSB, attains 1% of the crest value Vc.

Quantization error of a front-chopped LI test voltage due to the analogue–digital conversion

To validate the measuring uncertainty, various calibration procedures are recommended in IEC 61083-1:2001, which refer to both the hardware and the software. To validate the uncertainty caused by the hardware, the differential non-linearity

(DNL) as well as the integral non-linearity (INL) have to be determined using an “ideal” ADC as reference. The transfer function of such a reference ADC is characterized by a stepwise-increasing output code k = 1, 2 … 2N, where the input voltage is increased stepwise by  That means, for an output code

That means, for an output code  one gets for the next step

one gets for the next step  Here are Vin—the input voltage, Vfsd—the full-scale deflection voltage and N—the resolution in terms of bit.

Here are Vin—the input voltage, Vfsd—the full-scale deflection voltage and N—the resolution in terms of bit.

Estimation of the differential non-linearity given by w(k) − w(r) and integral non-linearity s(k) given by the deviation of the actual input voltage from the reference voltage of an “ideal” ADC

Comparison of a sin-shape input voltage with the output code of a non-linear 4-bit ADC

- 1.

Apply a precise sine wave of low frequency (e.g. 50 Hz) and adjust the amplitude close to the full-scale deflection (e.g. between −10 V and +10 V).

- 2.

Record in total ten periods of the applied AC voltage.

- 3.

Compare the count of occurrences of each code (code rate) with the ideal number of occurrences.

- 4.

Divide each code rate by the number of recorded periods, i.e. n = 10 for the here-considered case.

- 5.

Calculate the differential non-linearity (DNL) for each code:

- 6.

Calculate the integral non-linearity (INL) for each code:

The test is passed if at full-scale deflection the requirements  and

and  are satisfied.

are satisfied.

Full lightning impulse voltage (LI)

Front-chopped lightning impulse voltage (LIC)

Tail-chopped lightning impulse voltage (LIC)

Oscillating lightning impulse voltage (OLI)

Switching impulse voltage (SI)

Oscillating switching impulse voltages (OSI).

Example Table 7.4 shows the comparison between the evaluated parameters of two reference LI wave shapes (wave shapes no. LI-A4 and LI-M7 of the test data generator (TDG)) and those required according to IEC 61083-2:2013. Whereas the evaluation of no. LI-A4 delivers results within the tolerance band required by the standard, not all parameters of no. LI-M7 are correctly determined. This means the software has to be improved before it can be applied for practical tests.Table 7.4Test of software with the test data generator (TDG) according to IEC 61083-2:2013

Reference number of IEC 61083-2

Parameter

IEC reference value

IEC acceptance limits

Example: evaluated values

Remarks

Test voltage value Vt

−856.01 kV

−(855.15…856.87) kV

−856.4 kV

Evaluation accepted

Front time T1

0.841 μs

(0.824…0.858) μs

0.851 μs

Evaluation accepted

Time to half-value T2

47. 80 μs

(47.32…48.28) μs

47.88 μs

Evaluation accepted

Relative over-shoot β

7.9%

(6.9…8.9) %

7.2%

Evaluation accepted

Test voltage value Vt

1272.3 kV

(1271.0…1273.5) kV

1272 kV

Evaluation accepted

Front time T1

1.482 μs

(1.452…1.512) μs

1.390 μs

Evaluation rejecteda

Time to half-value T2

50.03 μs

(49.53…50.53) μs

5 0.10 μs

Evaluation accepted

Relative over-shoot β

11.2%

(10.2…12.2) %

9.9%

Evaluation rejecteda

Generally, it can be stated that the measurement of the peak value of full LI test voltages at measuring uncertainty of 2% is accomplished when the amplitude resolution amounts 10 bits and the sampling rate attains 100 MS/s, where the analogue bandwidth should not be lower than 100 MHz. Moreover, the integral non-linearity should be below 0.5%, and the internal background noise level should not exceed 0.4% of the full-scale deflection. For more information in this respect see Hällström (2002), Hällström et al. (2003), Wakimoto et al. (2007) and Schon (2013).

7.5 Measurement of High Currents in LI Voltage Tests

Voltage and current recorded during a LI withstand voltage test of a distribution transformer

The LI withstand test is passed when no significant differences are recognized between the normalized reference values and the normalized test values (IEC 60076-3:2013).

Basic components required for a LI current measuring system

Converting device, usually a shunt or even a fast current transformer to convert the transient current into a convenient measurable low voltage,

Transmission system, usually a BNC measuring cable or a fiber optic link,

Measuring instrument, usually a digital recorder.

Note The classic application of high current measurements is addressed to performance tests of protecting devices, such as lightning arresters, where peak values up to some hundreds of kA have to be measured. Measuring such high currents, however, is not the subject of this book. For more details in this respect, see IEC 62475:2012 and the series of the IEC 60099 standards.

To measure high-current pulses associated with LI voltage tests various types of converting devices are in use, such as resistive shunts, Rogowski coils, current transformers, hall-sensors, and magneto-optic sensors. In the following, however, only some particularities of resistive and inductive converting devices will be reviewed, which are mostly used for measuring high transient currents associated with LI withstand and breakdown tests.

7.5.1 Resistive Converting Device (Shunt)

superimposed on the resistive voltage signal

superimposed on the resistive voltage signal  , as qualitatively illustrated in Fig. 7.64.

, as qualitatively illustrated in Fig. 7.64.

Response of a current measuring system against an exponential rising current where the transducer was grounded via either a thin wire (left) or a low-inductive Cu foil (right)

Partial voltages vR(t) and vL(t) as well as the measurable voltage vm(t) = vR(t) + vL(t) appearing across a resistive shunt in case of an exponential rising current pulse

following from the time-dependent current

following from the time-dependent current  can be expressed by

can be expressed by

Equivalent circuit used to estimate the inductive voltage component vL(t) induced in the measuring loop between resistive shunt and BNC measuring cable

Example Consider a resistive shunt characterized by the following parameters:

Shunt resistance | Rs = 10 mΩ |

Shunt diameter | d = 10 mm |

Measuring loop | a = b = 50 mm |

![$$ v_{r} (t) = [(1\,{\text{kA}}) \cdot (10\,{\text{m}}\Omega )] \cdot [1 - exp (- t/\tau_{c} )] = (10\,{\text{V}}) \cdot [1 - exp( - t/\tau_{c} )] $$](../images/214133_2_En_7_Chapter/214133_2_En_7_Chapter_TeX_Equi.png)

Due to the above estimated inductance of Lm = 33 nH an inductive voltage component would be induced (Fig. 7.64). As the steepness attains a maximum value of 1 kA/2 μs = 0.5 kA/μs at the very beginning of the current pulse, the superimposed inductive voltage component would approach a crest value of Vc = (33 nH) · (0.5 kA/μs) = 16.5 V. Obviously, this is almost 70% greater than the maximum value, which attains a peak value of Vp = (1 kA) ∙ (10 mΩ) = 10 V across a pure resistive shunt.

7.5.2 Inductive Converting Device (Rogowski Coil)

Principle of impulse current measurement using inductive converting devices. a Single-turn current transducer. b Multiple-turn current transducer (Rogowski coil)

![$$ v_{l} \left( t \right) = M \cdot \frac{{{\text{d}}i}}{{{\text{d}}t}} = \left[ {\frac{{\mu_{0} \cdot n \cdot b}}{8} \cdot \ln \left( {\frac{2a + b}{2a - b}} \right)} \right] \cdot \frac{{{\text{d}}i}}{{{\text{d}}t}}, $$](../images/214133_2_En_7_Chapter/214133_2_En_7_Chapter_TeX_Equ47.png)

Transfer characteristics of a Rogowski coil

In principle the dynamic behaviour of Rogowski coils is comparable to that of a high-pass filter, i.e. a stationary direct current is not measurable. Consequently, the measuring error increases at decreasing frequency content and thus at increasing length of the current pulse (Fig. 7.68). To reduce the lower-limit frequency, the coil inductance must be increased accordingly, which can effectively be achieved by winding the turns around a high-permeable core. Based on practical experience it can be stated that Rogowski coils are capable of measuring current pulses up to 100 kA/μs, where the pulse duration is limited below some tens of µs. Using classical current transformers, pulse lengths up to the ms range can be captured at reasonable measuring uncertainty, while the steepness is limited to approx 1 kA/μs.

Dynamic behavior of a current transformer at fast rising (left) and a slowly rising (right) primary current

Dynamic behavior of a current transformer subjected to linearly rising and decaying current ramps at repetition rates of 5.4 MHz (left) and 0.54 MHz (right)

7.6 PD Measurement at Impulse Voltages

From a physical point of view, PD measurements of HV equipment should be carried out under test voltages, which are representative for service conditions. This is the reason why the relevant standard IEC 60270:2000 is mainly addressed to the measurement of partial discharges under power frequency AC voltages, see Sect. 4.3. As known, under service condition the insulation of HV equipment is not only stressed by the continuously applied operation voltage but also by different kinds of over-voltages, such as switching impulse (SI) and lightning impulse (LI) voltages as well as very fast front (VFF) voltages. In the following specific aspects of PD measurements under such kinds of test voltages will briefly be highlighted.

7.6.1 SI Test Voltages

In the late 1980s, when paper-insulated lead-covered cables (PILC) were increasingly substituted by cross-linked polyethylene-insulated (XLPE) cables, the measurement of partial discharges became an inevitable tool for quality assurance tests of XLPE cables performed not only in laboratory after manufacturing but also in the field after installation. The reason for that was the fact that the high-polymeric insulation is very sensitive to partial discharges, because a PD activity in the pC range causes already irreversible degradation processes. However, energizing the comparatively high cable capacitance by the use of classical AC test transformers needs a high power and is thus very expensive, in particular if PD tests are performed under on-site condition. Therefore, to reduce the test expenditure, the feasibility of alternative test voltages have been extensively investigated (Dorison and Aucort 1984; Auclair et al. 1988; Lefèvre et al. 1989). Among others the use of switching impulse (SI) voltages has been found as a promising alternative due to the fact that the PD signatures of internal discharges are quite well comparable to those encountered under power frequency AC voltage (Lemke et al. 1987).

SI voltage circuit for PD measurement. a Simplified block diagram of a single-stage SI generator. b Record of characteristic voltages with a 1 μF surge capacitor and a 0.22 μF cable capacitance. c Record gained for 1-μF cable capacitance

Example Fundamental PD studies under SI voltages revealed that potential PD defects in extruded power cables can be recognized at reasonable probability when the peak value of the applied SI voltage attains twice the phase-to-earth voltage, where the latter is expressed in terms of rms. Testing, for instance, a 12/20 kV XLPE cable of 1 km in length, a cable capacitance of nearly 0.2 µF must be charged up to a SI crest value of 24 kV. Using a single-stage SI generator according to Fig. 7.71, which is equipped with a 1 µF surge capacitor and a front resistor of 5.6 kΩ, the utilization factor attains 0.8, as obvious from the oscilloscopic screenshot shown in Fig. 7.71b. Consequently, the 1 μF surge capacitor must be charged up to a crest voltage of 31 kV to accomplish the desired SI crest voltage of 24 kV. Testing a cable of 5 km in length, a cable capacitance of approx. 1 μF must be charged. Under this condition, the utilization factor approaches 0.45, that means to accomplish the desired SI test voltage of 24 kV the 1 µF surge capacitor of the SI generator must be charged up to a crest voltage of 53 kV, see Fig. 7.71c.

PD signatures caused by an artificial cavity implemented in a cable sample at SI voltages of different steepness and almost identical peak values. a Rise time 400 μs, test voltage level 12 kV. b Rise time 1,600 µs, test voltage level 12.4 kV

Reproducibility of accumulated PD charges. a PD pulse train during the front time of an SI voltage. b–f Accumulated pulse charges recorded at identical front time and test voltage level (time scale: 200 μs/div, voltage scale: 4 kV/div, front time 1.6 ms, test voltage level 12.4 kV)

7.6.2 DAC Test Voltages

Block diagram of a DAC test generator (a) and characteristic oscilloscopic record (b) showing the continuous rising DC stress and the damped AC voltage occurring just after the sphere spark gap has been triggered

Block diagram of a DAC test facility used for fundamental PD studies

Phase-resolved PD patterns of void discharges in a cable sample. a Continuous 50-Hz AC voltage. b 80-Hz DAC voltage stress displayed for the first positive voltage sweep. c 80-Hz DAC voltage stress displayed for the first negative voltage sweep

Pulse charge magnitudes measured for a MV cable termination. a Damped AC voltage of 80 Hz. b Continuous AC voltage of 50 Hz

PD signatures of a defective 20-kV cable termination at DAC test voltage using DC voltage ramps of 10, 50, and 250 μs rise time (from left to right)

7.6.3 Short Impulse Voltages (LI and VFF Test Voltages)

Lichtenberg figures (fotograms) of streamer filaments developing in a 20 cm cone-plane air gap under SI voltage (a) and steep front voltage (b) and associated oscilloscopic records (Lemke 1967), explanation in the text

Impact of the front time of SI voltages on the PD signature of a cavity discharge. a 8 μs front time, 11.6 kV test voltage. b 3 μs front time, 11 kV test voltage